Ddr2 synch dram

DRAM integrated circuits ICs produced from the early s to early s used an asynchronous interface, in which input control signals have a direct effect on internal functions only delayed by the trip across its semiconductor pathways, ddr2 synch dram.

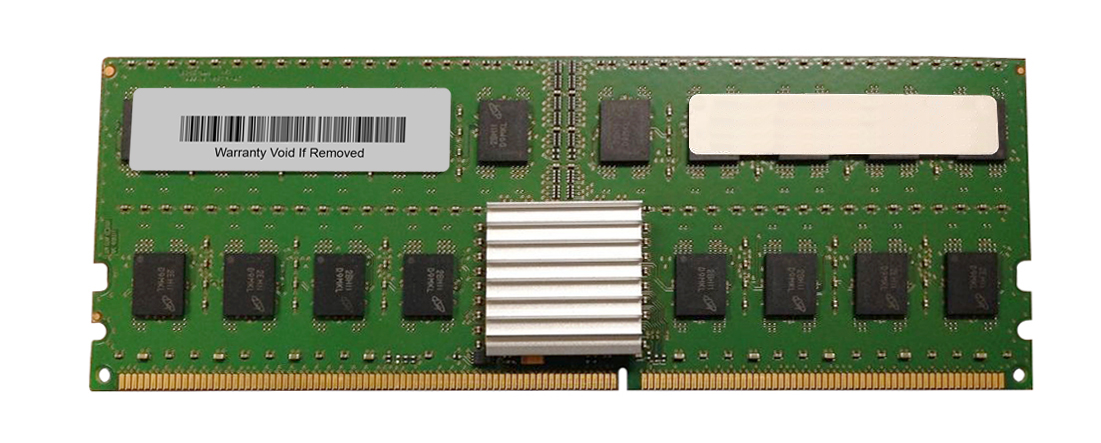

Traditionally, dynamic random access memory DRAM had an asynchronous interface, which means that it responds as quickly as possible to changes in control inputs. This allows the memory chip to have a more complex pattern of operation than an asynchronous DRAM. DDR stands for double data rate, which means the chip reads or writes two words of data per clock cycle. The DDR interface accomplishes this by reading and writing data on both the rising and falling edges of the clock signal. In addition, some minor changes to the SDR interface timing were made in hindsight, and the supply voltage was reduced from 3. In a computer system, the clock signal is an oscillating frequency used to coordinate interaction between digital circuits. Simply put, it synchronizes communication.

Ddr2 synch dram

Supreme shock-resistant qualities ensure superior protection for data stored on the drive. The DrivePro is an ultimate pair of dashcams including a front camera and a rear camera. Featuring high-sensitivity image sensors, it delivers crystal clear sharpness and night images even in low light. With built-in safety functions like a head-up display, emergency recording, and more, the DrivePro is bound to protect your journey all round. With a USB 3. High capacity of up to GB creates sufficient storage space for media files and gaming files. If you are searching for a portable and stylish storage device to play games, Transcend's JetFlash C is the one! Its compact form factor, high compatibility, and outstanding performance are ideal for embedded applications in the medical, military, and automation sectors. They are ideal for write-intensive applications such as medical devices, surveillance systems, and POS terminals. This enables the memory controller to know the exact clock cycle when the requested data will be ready, so the CPU no longer has to wait between memory accesses.

While self-refresh mode consumes slightly more power than power-down mode, it allows the memory controller to be disabled entirely, which commonly more than makes up the difference. However, once a ddr2 synch dram is read, subsequent column accesses to that same row can be very quick, as the sense amplifiers also act as latches.

In addition to double pumping the data bus as in DDR SDRAM transferring data on the rising and falling edges of the bus clock signal , DDR2 allows higher bus speed and requires lower power by running the internal clock at half the speed of the data bus. The two factors combine to produce a total of four data transfers per internal clock cycle. Alternatively, DDR2 memory operating at twice the external data bus clock rate as DDR may provide twice the bandwidth with the same latency. Both performed worse than the original DDR specification due to higher latency, which made total access times longer. These chips are mostly standard DDR chips that have been tested and rated to be capable of operation at higher clock rates by the manufacturer. Such chips draw significantly more power than slower-clocked chips, but usually offered little or no improvement in real-world performance. DDR2 started to become competitive against the older DDR standard by the end of , as modules with lower latencies became available.

Search Everywhere Threads This forum This thread. Search titles only. Search Advanced search…. Everywhere Threads This forum This thread. Search Advanced…. Log in. Install the app. New posts Search forums.

Ddr2 synch dram

Implementations often have to use schemes such as phase-locked loops and self-calibration to reach the required timing accuracy. One advantage of keeping the clock frequency low is that it reduces the signal integrity requirements on the circuit board connecting the memory to the controller. The first specification is for memory chips, and the second is for memory modules.

Xvideos belami

Featuring high-sensitivity image sensors, it delivers crystal clear sharpness and night images even in low light. DDR2 started to become competitive against the older DDR standard by the end of , as modules with lower latencies became available. The bus protocol was also simplified to allow higher performance operation. Each bank group has the feature of singlehanded operation. A write command is accompanied by the data to be written driven on to the DQ lines during the same rising clock edge. With a USB 3. This enables the memory controller to know the exact clock cycle when the requested data will be ready, so the CPU no longer has to wait between memory accesses. These chips cannot achieve the clock rates of GDDR3 but are inexpensive and fast enough to be used as memory on mid-range cards. There is actually a 17th "dummy channel" used for some operations. If you read this far, you should follow us:. Again, with every doubling, the downside is the increased latency. Archived from the original on December 19, Although refreshing a row is an automatic side effect of activating it, there is a minimum time for this to happen, which requires a minimum row access time t RAS delay between an active command opening a row, and the corresponding precharge command closing it. Archived PDF from the original on

Some confusion has been created due to the difference in the listings for speed "MHz" , and the way memory is described from a sales standpoint " personal computer XXXXXX ".

Embedded SSD Solutions. In development. Read Edit View history. You have already accepted cookies, but you may still revoke your consent at any time. There were a number of 8-bit control registers and bit status registers to control various device timing parameters. Subsequent words of the burst will be produced in time for subsequent rising clock edges. It was revealed at the Intel Developer Forum in San Francisco in , and was due to be released to market during Modules with multiple DRAM chips can provide correspondingly higher bandwidth. During these wait cycles, additional commands may be sent to other banks; because each bank operates completely independently. Wikimedia Commons. If the transmitted msbit was set, all least-significant bits up to and including the least-significant 0 bit of the transmitted address were ignored for "is this addressed to me? August The Inquirer.

0 thoughts on “Ddr2 synch dram”